# 32-bit Proprietary Microcontrollers

## FR60Lite MB91265A Series

### MB91266A/MB91F267A/MB91F267NA/MB91V265A

#### ■ DESCRIPTION

The MB91265A series is a 32-bit RISC microcontroller designed by Fujitsu for embedded control applications which require high-speed processing.

The CPU is used the FR family\* and the compatibility of FR60Lite.

MB91F267NA loads the C-CAN (1 channel) .

\*: FR, the abbreviation of FUJITSU RISC controller, is a line of products of FUJITSU Limited.

### **■ FEATURES**

- FR60Lite CPU

- 32-bit RISC, load/store architecture with a five-stage pipeline

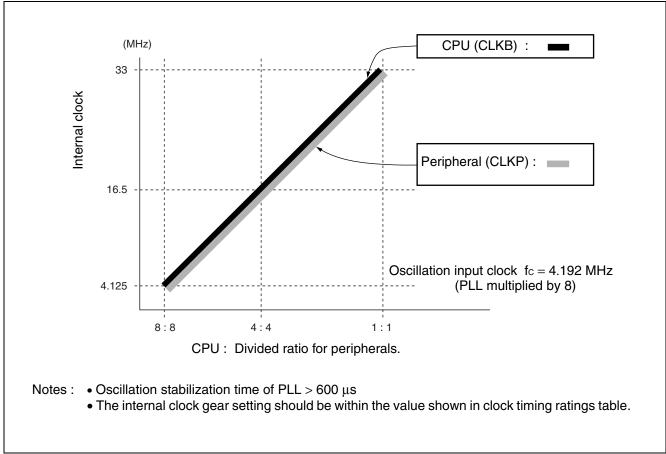

- Maximum operating frequency: 33 MHz (oscillation frequency 4.192 MHz, oscillation frequency 8-multiplier (PLL clock multiplication method)

- 16-bit fixed length instructions (basic instructions)

- Execution speed of instructions : 1 instruction per cycle

- Memory-to-memory transfer, bit handling, barrel shift instructions, etc.: Instructions suitable for embedded applications

- Function entry/exit instructions, multiple-register load/store instructions: Instructions adapted for C-language

- Register interlock function : Facilitates coding in assembler.

- Built-in multiplier with instruction-level support

- 32-bit multiplication with sign : 5 cycles

- 16-bit multiplication with sign : 3 cycles

- Interrupt (PC, PS save): 6 cycles, 16 priority levels

- · Harvard architecture allowing program access and data access to be executed simultaneously

- Instruction compatible with FR family

(Continued)

Be sure to refer to the "Check Sheet" for the latest cautions on development.

"Check Sheet" is seen at the following support page

URL: http://www.fujitsu.com/global/services/microelectronics/product/micom/support/index.html

"Check Sheet" lists the minimal requirement items to be checked to prevent problems beforehand in system development.

(Continued)

- Internal peripheral functions

- Capacity of internal ROM and ROM type

MASK ROM: 64 Kbytes (MB91266A)

Flash ROM: 128 Kbytes (MB91F267A/MB91F267NA)

: 24 Kbytes (evaluation model\*)

- \*: Evaluation model is MB91V265A.

- Capacity of internal RAM: 2 Kbytes (MASK product)/4 Kbytes (Flash memory product)

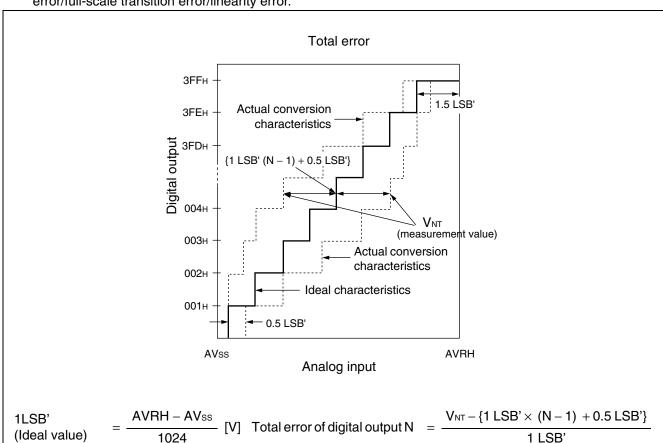

- A/D converter (sequential comparison type)

Resolution: 8/10 bits: 4 channels  $\times$  1 unit, 7 channels  $\times$  1 unit

Conversion time: 1.2 µs (Minimum conversion time system clock at 33 MHz)

1.35 μs (Minimum conversion time system clock at 20 MHz)

- External interrupt input : 8 channels

- Bit search module (for REALOS)

Function for searching the MSB (upper bit) in each word for the first 1-to-0 inverted bit position

- C-CAN 32MSB: 1 channel (loaded in MB91F267NA only)

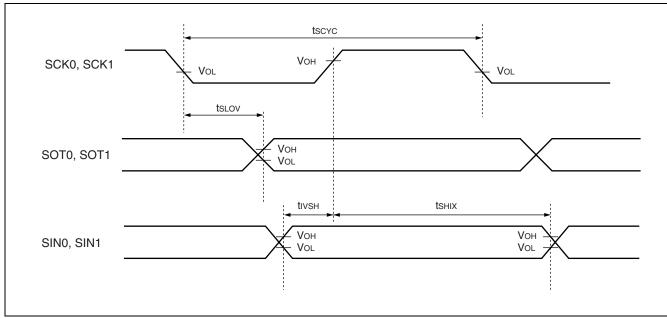

- UART (Full-duplex double buffer): 2 channels

Selectable parity On/Off

Asynchronous (start-stop synchronized) or clock-synchronous communications selectable

Internal timer for dedicated baud rate (U-TIMER) on each channel

External clock can be used as transfer clock

Error detection function for parity, frame, and overrun errors

- 8/16-bit PPG timer: 8 channels (at 8-bit) / 4 channels (at 16-bit)

- Timing generator

- 16-bit reload timer: 3 channels (with cascade mode, without output of reload timer 0)

- 16-bit free-run timer: 3 channels

- 16-bit PWC timer: 1 channel

- Input capture: 4 channels (interface with free-run timer)

- Output compare : 6 channels (interface with free-run timer)

- Waveform generator

Various waveforms which are generated by using output compare, 16-bit PPG timer 0, and 16-bit dead timer

· SUM of products macro

RAM : instruction RAM (I-RAM)  $256 \times 16$ -bit coefficient RAM (X-RAM)  $64 \times 16$ -bit variable RAM (Y-RAM)  $64 \times 16$ -bit

Execution of 1 cycle MAC (16-bit × 16-bit + 40 bits)

Operation results are extracted rounded from 40 to 16 bits

• DMAC (DMA Controller) : 5 channels

Operation of transfer and activation by internal peripheral interrupts and software

- · Watchdog timer

- Low-power consumption mode

Sleep/stop function

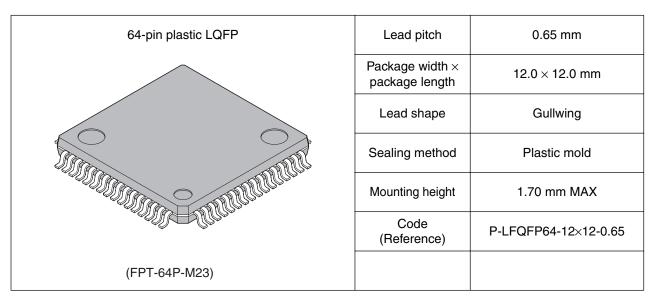

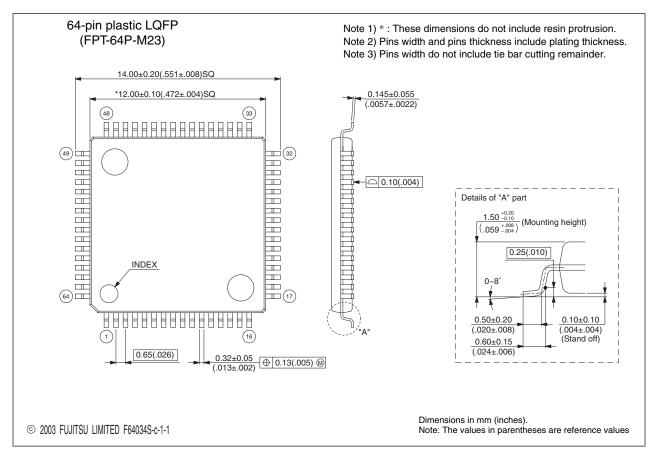

- Package : LQFP-64P

- Technology: CMOS 0.35 μm

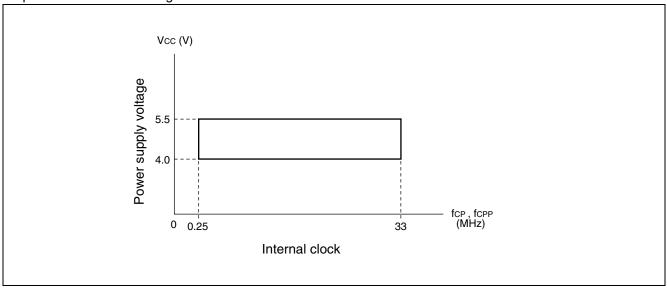

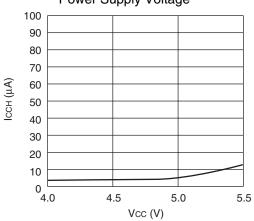

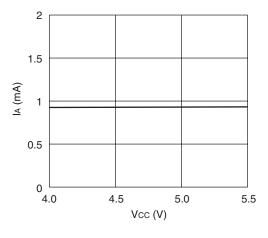

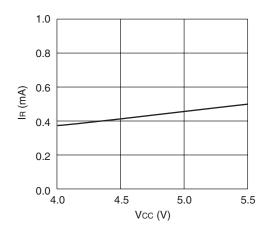

- Power supply : 1-power supply (Vcc = 4.0 V to 5.5 V)

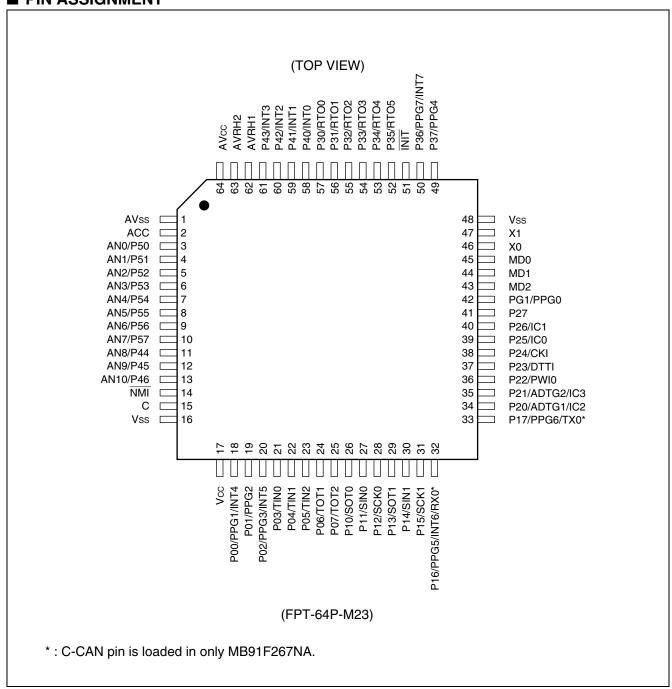

### **■ PIN ASSIGNMENT**

### **■ PIN DESCRIPTION**

| Pin no. | Pin<br>name | I/O<br>Circuit<br>type*1 | Description                                                                                                                       |  |  |

|---------|-------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--|--|

| 3       | AN0         | G                        | Analog input terminal of A/D converter 1.  This function becomes valid when set the corresponding AICR1 register to analog input. |  |  |

| 3       | P50         | G                        | General purpose input/output port. This function becomes valid when analog input is set to disabled.                              |  |  |

| 4       | AN1         | G                        | Analog input terminal of A/D converter 1. This function becomes valid when set the corresponding AICR1 register to analog input.  |  |  |

| 7       | P51         | u                        | General purpose input/output port. This function becomes valid when analog input is set to disabled.                              |  |  |

| 5       | AN2         | G                        | Analog input terminal of A/D converter 1. This function becomes valid when set the corresponding AICR1 register to analog input.  |  |  |

| 5       | P52         | G                        | General purpose input/output port. This function becomes valid when analog input is set to disabled.                              |  |  |

| 6       | AN3         | G                        | Analog input terminal of A/D converter 1. This function becomes valid when set the corresponding AICR1 register to analog input.  |  |  |

| 6       | P53         | G                        | General purpose input/output port. This function becomes valid when analog input is set to disabled.                              |  |  |

| 7       | AN4         | G                        | Analog input terminal of A/D converter 2. This function becomes valid when set the corresponding AICR2 register to analog input.  |  |  |

| ,       | P54         |                          | General purpose input/output port. This function becomes valid when analog input is set to disabled.                              |  |  |

| 8       | AN5         | G                        | Analog input terminal of A/D converter 2. This function becomes valid when set the corresponding AICR2 register to analog input.  |  |  |

| 0       | P55         | G                        | General purpose input/output port. This function becomes valid when analog input is set to disabled.                              |  |  |

| 0       | AN6         | G                        | Analog input terminal of A/D converter 2. This function becomes valid when set the corresponding AICR2 register to analog input.  |  |  |

| 9       | P56         | G                        | General purpose input/output port. This function becomes valid when analog input is set to disabled.                              |  |  |

| 10      | AN7         | G                        | Analog input terminal of A/D converter 2. This function becomes valid when set the corresponding AICR2 register to analog input.  |  |  |

| 10      | P57         | G                        | General purpose input/output port. This function becomes valid when analog input is set to disabled.                              |  |  |

| 11      | AN8         | G                        | Analog input terminal of A/D converter 2. This function becomes valid when set the corresponding AICR2 register to analog input.  |  |  |

| 11      | P44         | G                        | General purpose input/output port. This function becomes valid when analog input is set to disabled.                              |  |  |

| 10      | AN9         | C                        | Analog input terminal of A/D converter 2. This function becomes valid when set the corresponding AICR2 register to analog input.  |  |  |

| 12      | P45         | G<br>45                  | General purpose input/output port. This function becomes valid when analog input is set to disabled.                              |  |  |

| Pin no. | Pin<br>name | I/O<br>Circuit<br>type*1 | Description                                                                                                                                                                                |  |  |

|---------|-------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 13      | AN10        | G                        | Analog input terminal of A/D converter 2. This function becomes valid when set the corresponding AICR2 register to analog input.                                                           |  |  |

|         | P46         |                          | General purpose input/output port. This function becomes valid when analog input is set to disabled.                                                                                       |  |  |

| 14      | NMI         | Н                        | NMI (Non Maskable Interrupt) input terminal.                                                                                                                                               |  |  |

|         | INT4        |                          | External interrupt input terminal.  Since this input is used as required while the corresponding external interrupt is enabled, the port output must remain off unless intentionally used. |  |  |

| 18      | PPG1        | E                        | Output terminal of PPG timer 1. This function becomes valid when output of PPG timer 1 is set to enabled.                                                                                  |  |  |

|         | P00         |                          | General purpose input/output port. This function becomes valid when output of PPG timer 1 and external interrupt input are set to disabled.                                                |  |  |

| 19      | PPG2        | D                        | Output terminal of PPG timer 2. This function becomes valid when output of PPG timer 2 is set to enabled.                                                                                  |  |  |

| 19      | P01         |                          | General purpose input/output port. This function becomes valid when output of PPG timer 2 is set to disabled.                                                                              |  |  |

|         | INT5        |                          | External interrupt input terminal. Since this input is used as required while the corresponding external interrupt is enabled, the port output must remain off unless intentionally used.  |  |  |

| 20      | PPG3        | E                        | Output terminal of PPG timer 3. This function becomes valid when output of PPG timer 3 is set to enabled.                                                                                  |  |  |

|         | P02         |                          | General purpose input/output port. This function becomes valid when output of PPG timer 3 and external interrupt input are set to disabled.                                                |  |  |

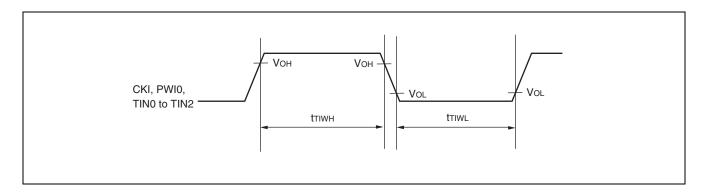

| 21      | TIN0        | -                        | External trigger input terminal of reload timer 0.<br>Since this input is used as required while the trigger input is enabled, the port output must remain off unless intentionally used.  |  |  |

| 21      | P03         | D                        | General purpose input/output port. This function becomes valid when external clock input of reload timer 0 is set to disabled.                                                             |  |  |

| 22      | TIN1        | D                        | External trigger input terminal of reload timer 1. Since this input is used as required while the trigger input is enabled, the port output must remain off unless intentionally used.     |  |  |

| 22 –    | P04         | D                        | General purpose input/output port. This function becomes valid when external clock input of reload timer 1 is set to disabled.                                                             |  |  |

| 23      | TIN2        | D                        | External trigger input terminal of reload timer 2. Since this input is used as required while the trigger input is enabled, the port output must remain off unless intentionally used.     |  |  |

| 20      | P05         | 0                        | General purpose input/output port. This function becomes valid when external clock input of reload timer 2 is set to disabled.                                                             |  |  |

| Pin no. | Pin<br>name | I/O<br>Circuit<br>type*1 | Description                                                                                                                                                  |

|---------|-------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 24      | TOT1        | D                        | Output terminal of reload timer 1. This function becomes valid when output of reload timer 1 is set to enabled.                                              |

| 24      | P06         | D                        | General purpose input/output port. This function becomes valid when output of reload timer 1 is set to disabled.                                             |

| 25      | ТОТ2        | D                        | Output terminal of reload timer 2. This function becomes valid when output of reload timer 2 is set to enabled.                                              |

| 25      | P07         | D                        | General purpose input/output port. This function becomes valid when output of reload timer 2 is set to disabled.                                             |

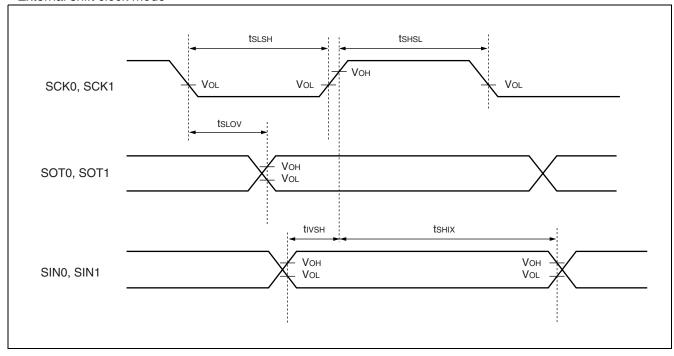

| 26      | SOT0        | D                        | UART0 data output terminal. This function becomes valid when data output of UART0 is set to enabled.                                                         |

| 20      | P10 D       |                          | General purpose input/output port. This function becomes valid when data output of UART0 is set to disabled.                                                 |

| 27      | SIN0        | D                        | UART0 data input terminal. Since this input is used as required while the UART0 input is enabled, the port output must remain off unless intentionally used. |

|         | P11         |                          | General purpose input/output port. This function becomes valid when data input of UART0 is set to disabled.                                                  |

| 28      | SCK0        | D                        | UART0 clock input/output terminal. This function becomes valid when clock output of UART0 is set to enabled.                                                 |

| 20      | P12         |                          | General purpose input/output port. This function becomes valid when clock output of UART0 is set to disabled.                                                |

| 29      | SOT1        | D                        | UART1 data output terminal. This function becomes valid when data output of UART1 is set to enabled.                                                         |

| 29      | P13         | D                        | General purpose input/output port. This function becomes valid when data output of UART1 is set to disabled.                                                 |

| 30      | SIN1        | D                        | UART1 data input terminal. Since this input is used as required while the UART1 input is enabled, the port output must remain off unless intentionally used. |

|         | P14         |                          | General purpose input/output port. This function becomes valid when data input of UART1 is set to disabled.                                                  |

| 31      | SCK1        | D                        | UART1 clock input/output terminal. This function becomes valid when clock output of UART1 is set to enabled.                                                 |

| 31      | P15         | P15                      | General purpose input/output port. This function becomes valid when clock output of UART1 is set to disabled.                                                |

| Pin no. | Pin<br>name | I/O<br>Circuit<br>type*1 | Description                                                                                                                                                                                                                                                                                            |  |  |

|---------|-------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|         | INT6        |                          | External interrupt input terminal. Since this input is used as required while the corresponding external interrupt is enabled, the port output must remain off unless intentionally used.                                                                                                              |  |  |

|         | PPG5        |                          | Output terminal of PPG timer 5. This function becomes valid when output of PPG timer 5 is set to enabled.                                                                                                                                                                                              |  |  |

| 32      | RX0         | E                        | RX0 input terminal of C-CAN0 (MB91F267NA only ) . Since this input is used as required while the RX0 input is enabled, port output must remain off unless intentionally used.                                                                                                                          |  |  |

|         | P16         |                          | General purpose input/output port.  This function becomes valid when output of PPG timer 5 and RX0 input*2 of C-CAN0 are set to disabled.                                                                                                                                                              |  |  |

|         | PPG6        |                          | Output terminal of PPG timer 6. This function becomes valid when output of PPG timer 6 is set to enabled.                                                                                                                                                                                              |  |  |

| 33      | TX0         | D                        | TX0 output terminal of C-CAN0 (only MB91F267NA) . This function becomes valid when TX0 output of C-CAN0 is set to enabled.                                                                                                                                                                             |  |  |

|         | P17         |                          | General purpose input/output port.  This function becomes valid when output of PPG timer 6 and TX0 output*2 of C-CAN0 are set to disabled.                                                                                                                                                             |  |  |

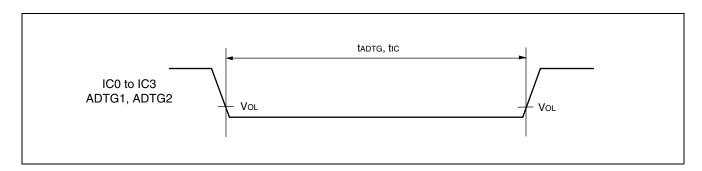

|         | ADTG1       | D                        | External trigger input terminal of A/D converter 1.<br>Since this input is used as required while it selects as A/D activation trigger cause, the port output must remain off unless intentionally used.                                                                                               |  |  |

| 34      | IC2         |                          | Trigger input terminal of input capture 2.  The port can serve as an input when set for input with the setting of the input capture trigger input. When the port is used for input capture input, this input is used as required. The port output must therefore remain off unless intentionally used. |  |  |

|         | P20         |                          | General purpose input/output port.  This function becomes valid when the setting of the external trigger input of A/D converter 1 or the setting of the input capture trigger input is set to disabled.                                                                                                |  |  |

|         | ADTG2       | D                        | External trigger input terminal of A/D converter 2. Since this input is used as required while it selects as A/D activation trigger cause, the port output must remain off unless intentionally used.                                                                                                  |  |  |

| 35      | IC3         |                          | Trigger input terminal of input capture 3.  The port can serve as an input when set for input with the setting of the input capture trigger input. When the port is used for input capture input, this input is used as required. The port output must therefore remain off unless intentionally used. |  |  |

|         | P21         |                          | General purpose input/output port.  This function becomes valid when the setting of the external trigger input of A/D converter 2 or the setting of the input capture trigger input is set to disabled.                                                                                                |  |  |

| 36      | PWI0        | D                        | Pulse width counter input of PWC timer 0 This function becomes valid when pulse width counter input of PWC timer 0 is set to enabled.                                                                                                                                                                  |  |  |

| 30      | P22         | U                        | General purpose input/output port. This function becomes valid when pulse width counter input of PWC timer 0 is set to disabled.                                                                                                                                                                       |  |  |

| Pin no. | Pin<br>name | I/O<br>Circuit<br>type*1 | Description                                                                                                                                                                                                                                                                                                 |  |

|---------|-------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 37      | DTTI        | D                        | Control input signal of multi-function timer waveform generator output RTO0 to RTO5. This function becomes valid when DTTI input is set to enabled.                                                                                                                                                         |  |

| 37      | P23         | ם                        | General purpose input/output port. This function becomes valid when input of DTTI is set to disabled.                                                                                                                                                                                                       |  |

| 38      | CKI         | D                        | External clock input terminal of free-run timer.  Since this input is used as required while the port is used for external clock input terminal of free-run timer, the port output must remain off unless intentionally used.                                                                               |  |

| 00      | P24         | J                        | General purpose input/output port. This function becomes valid when external clock input of free-run timer is set to disabled.                                                                                                                                                                              |  |

| 39      | IC0         | D                        | Trigger input terminal of input capture 0.  The port can serve as an input when set for input with the setting of the trigger input of input capture 0. When the port is used for input capture input, this input is used as required. The port output must therefore remain off unless intentionally used. |  |

|         | P25         |                          | General purpose input/output port. This function becomes valid when trigger input of input capture 0 is set to disabled.                                                                                                                                                                                    |  |

| 40      | IC1         | D                        | Trigger input terminal of input capture 1.  The port can serve as an input when set for input with the setting of the trigger input of input capture 1. When the port is used for input capture input, this input is used as required. The port output must therefore remain off unless intentionally used. |  |

|         | P26         |                          | General purpose input/output port.  This function becomes valid when trigger input of input capture 1 is set to disabled.                                                                                                                                                                                   |  |

| 41      | P27         | D                        | General purpose input/output port.                                                                                                                                                                                                                                                                          |  |

| 42      | PPG0        |                          | Output terminal of PPG timer 0. This function becomes valid when output of PPG timer 0 is set to enabled.                                                                                                                                                                                                   |  |

| 42      | PG1         | D                        | General purpose input/output port. This function becomes valid when output of PPG timer 0 is set to disabled.                                                                                                                                                                                               |  |

| 43      | MD2         | H, K                     | Mode terminal 2. Setting this pin determines the basic operation mode. Connect to Vcc or Vss. The circuit type of flash memory models is K.                                                                                                                                                                 |  |

| 44      | MD1         | H, K                     | Mode terminal 1. Setting this pin determines the basic operation mode. Connect to Vcc or Vss. The circuit type of flash memory models is K.                                                                                                                                                                 |  |

| 45      | MD0         | Н                        | Mode terminal 0. Setting this pin determines the basic operation mode. Connect to Vcc or Vss.                                                                                                                                                                                                               |  |

| 46      | X0          | Α                        | Clock (oscillation) input terminal.                                                                                                                                                                                                                                                                         |  |

| 47      | X1          | Α                        | Clock (oscillation) output terminal.                                                                                                                                                                                                                                                                        |  |

| 49      | PPG4        | D                        | Output terminal of PPG timer 4. This function becomes valid when output of PPG timer 4 is set to enabled.                                                                                                                                                                                                   |  |

| 43      | P37         | D                        | General purpose input/output port. This function becomes valid when output of PPG timer 4 is set to disabled.                                                                                                                                                                                               |  |

| Pin no. | Pin<br>name | I/O<br>Circuit<br>type*1 | Description                                                                                                                                                                                                                     |  |  |

|---------|-------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|         | INT7        |                          | External interrupt input terminal. Since this input is used as required while the corresponding external interrupt is enabled, the port output must remain off unless intentionally used.                                       |  |  |

| 50      | PPG7        | Е                        | Output terminal of PPG timer 7. This function becomes valid when output of PPG timer 7 is set to enabled.                                                                                                                       |  |  |

|         | P36         |                          | General purpose input/output port. This function becomes valid when output of PPG timer 7 is set to disabled.                                                                                                                   |  |  |

| 51      | TINI        | I                        | External reset input terminal.                                                                                                                                                                                                  |  |  |

| 52      | RTO5        | J                        | Waveform generator output terminal of multi-function timer. This terminal outputs waveform set at the waveform generator. This function becomes valid when waveform generator output of multi-function timer is set to enabled. |  |  |

|         | P35         |                          | General purpose input/output port. This function becomes valid when output of waveform generator is set to disabled.                                                                                                            |  |  |

| 53      | RTO4        | J                        | Waveform generator output terminal of multi-function timer. This terminal outputs waveform set at the waveform generator. This function becomes valid when waveform generator output of multi-function timer is set to enabled. |  |  |

|         | P34         |                          | General purpose input/output port. This function becomes valid when output of waveform generator is set to disabled.                                                                                                            |  |  |

| 54      | RTO3        | J                        | Waveform generator output terminal of multi-function timer. This terminal outputs waveform set at the waveform generator. This function becomes valid when waveform generator output of multi-function timer is set to enabled. |  |  |

|         | P33         |                          | General purpose input/output port. This function becomes valid when output of waveform generator is set to disabled.                                                                                                            |  |  |

| 55      | RTO2        | J                        | Waveform generator output terminal of multi-function timer. This terminal outputs waveform set at the waveform generator. This function becomes valid when waveform generator output of multi-function timer is set to enabled. |  |  |

|         | P32         |                          | General purpose input/output port. This function becomes valid when output of waveform generator is set to disabled.                                                                                                            |  |  |

| 56      | RTO1        | J                        | Waveform generator output terminal of multi-function timer. This terminal outputs waveform set at the waveform generator. This function becomes valid when waveform generator output of multi-function timer is set to enabled. |  |  |

|         | P31         |                          | General purpose input/output port. This function becomes valid when output of waveform generator is set to disabled.                                                                                                            |  |  |

| 57      | RTO0        | J                        | Waveform generator output terminal of multi-function timer. This terminal outputs waveform set at the waveform generator. This function becomes valid when waveform generator output of multi-function timer is set to enabled. |  |  |

|         | P30         |                          | General purpose input/output port. This function becomes valid when output of waveform generator is set to disabled.                                                                                                            |  |  |

| 58      | INT0        | E                        | External interrupt input terminal. Since this input is used as required while the corresponding external interrupt is enabled, the port output must remain off unless intentionally used.                                       |  |  |

|         | P40         | P40                      | General purpose input/output port. This function becomes valid when external interrupt input is set to disabled.                                                                                                                |  |  |

(Continued)

| Pin no. | Pin<br>name | I/O<br>Circuit<br>type*1 | Description                                                                                                                                                                                |  |  |  |  |  |

|---------|-------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 59      | INT1 E      |                          | External interrupt input terminal. Since this input is used as required while the corresponding external interrupt is enabled, the port output must remain off unless intentionally used.  |  |  |  |  |  |

|         | P41         |                          | General purpose input/output port. This function becomes valid when external interrupt input is set to disabled.                                                                           |  |  |  |  |  |

| 60      | INT2        | E                        | External interrupt input terminal. Since this input is used as required while the corresponding external interrupt is enabled, the port output must remain off unless intentionally used.  |  |  |  |  |  |

|         | P42         |                          | General purpose input/output port. This function becomes valid when external interrupt input is set to disabled.                                                                           |  |  |  |  |  |

| 61      | INT3        | Е                        | External interrupt input terminal.  Since this input is used as required while the corresponding external interrupt is enabled, the port output must remain off unless intentionally used. |  |  |  |  |  |

|         | P43         |                          | General purpose input/output port. This function becomes valid when external interrupt input is set to disabled.                                                                           |  |  |  |  |  |

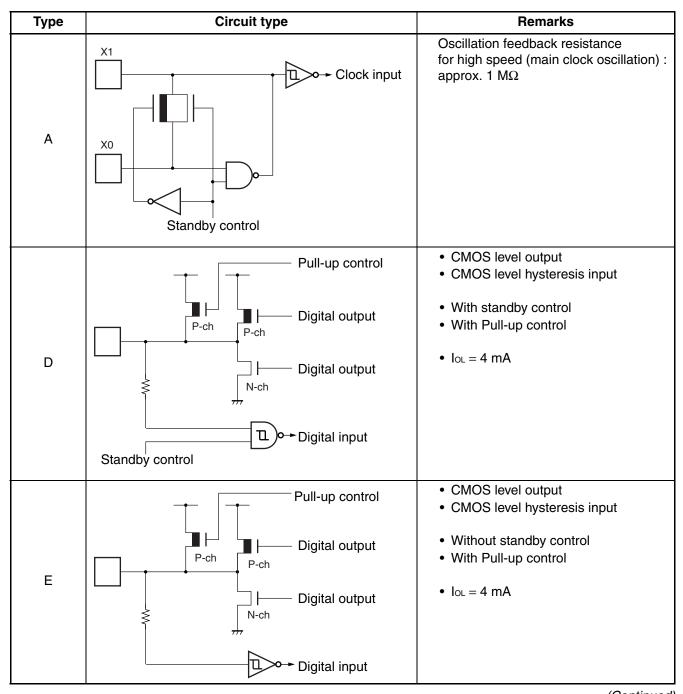

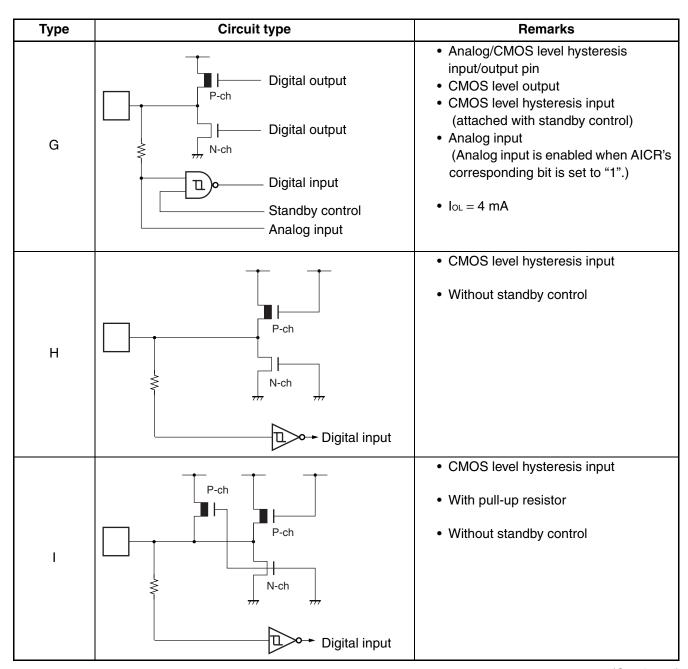

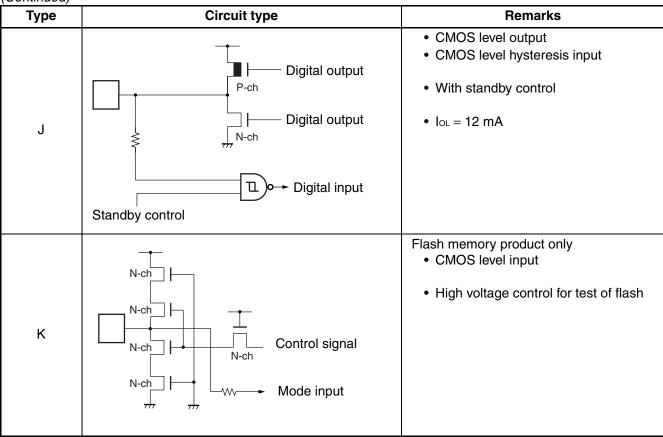

<sup>\*1 :</sup> For the I/O circuit type, refer to " ■ I/O CIRCUIT TYPE "

• Power supply and GND pins

| Pin no. | Pin name | Description                                                 |

|---------|----------|-------------------------------------------------------------|

| 16, 48  | Vss      | GND pins. Apply equal potential to all of the pins.         |

| 17      | Vcc      | Power supply pin. Apply equal potential to all of the pins. |

| 64      | AVcc     | Analog power supply pin for A/D converter.                  |

| 63      | AVRH2    | Analog reference power supply pin for A/D converter 2.      |

| 62      | AVRH1    | Analog reference power supply pin for A/D converter 1.      |

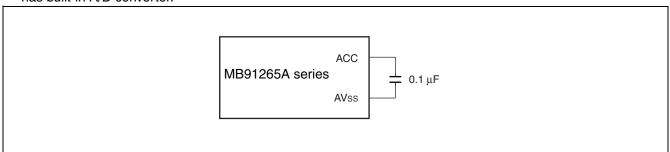

| 1       | AVss     | Analog GND pin for A/D converter.                           |

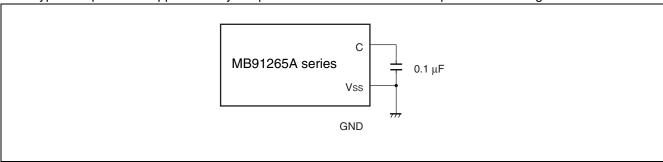

| 15      | С        | Condenser connection pin for internal regulator.            |

| 2       | ACC      | Condenser connection pin for analog.                        |

<sup>\*2 :</sup> C-CAN is set in only MB91F267NA.

### **■ I/O CIRCUIT TYPE**

### **■ HANDLING DEVICES**

#### **Preventing Latch-up**

Latch-up may occur in a CMOS IC if a voltage greater than Vcc pin or less than Vss pin is applied to an input or output pin or if an above-rating voltage is applied between Vcc and Vss pins.

A latch-up, if it occurs, significantly increases the power supply current and may cause thermal destruction of an element. When you use a CMOS IC, be very careful not to exceed the absolute maximum rating.

#### **Treatment of Unused Input Pins**

Do not leave an unused input pin open, since it may cause a malfunction. Handle by, for example, using a pull-up or pull-down resistor.

#### **About Power Supply Pins**

In products with multiple  $V_{\text{CC}}$  or  $V_{\text{SS}}$  pins, the pins of the same potential are internally connected in the device to avoid abnormal operations including latch-up. However, you must connect the pins to external power supply and a ground line to lower the electro-magnetic emission level, to prevent abnormal operation of strobe signals caused by the rise in the ground level, and to conform to the total output current rating.

Moreover, connect the current supply source with the Vcc and Vss pins of this device at the low impedance.

It is also advisable to connect a ceramic bypass capacitor of approximately 0.1  $\mu$ F between  $V_{\text{CC}}$  and  $V_{\text{SS}}$  pins near this device.

### **About Crystal Oscillator Circuit**

Noise near the X0 and X1 pins may cause the device to malfunction. Design the printed circuit board so that X0 and X1 pins the crystal oscillator (or ceramic oscillator) , and the bypass capacitor to ground are located as close to the device as possible.

It is strongly recommended to design the PC board artwork with the X0 and X1 pins surrounded by ground plane because stable operation can be expected with such a layout.

Please ask the crystal maker to evaluate the oscillational characteristics of the crystal and this device.

#### About Mode Pins (MD0 to MD2)

These pins should be connected directly to Vcc or Vss pins.

To prevent the device erroneously switching to test mode due to noise, design the printed circuit board such that the distance between the mode pins and  $V_{CC}$  or  $V_{SS}$  pins is as short as possible and the connection impedance is low.

#### **Operation at Start-up**

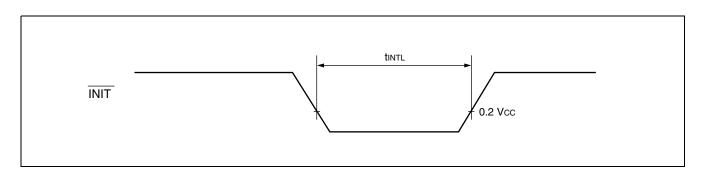

Be sure to execute setting initialized reset (INIT) with INIT pin immediately after start-up.

Also, in order to provide the oscillation stabilization wait time for the oscillation circuit immediately after start-up, hold the "L" level input to the  $\overline{\text{INIT}}$  pin for the required stabilization wait time (For INIT via the  $\overline{\text{INIT}}$  pin, the oscillation stabilization wait time setting is initialized to the minimum value) .

### Order of power turning ON/OFF

Use the following procedure for turning the power on or off.

Note that, even if the A/D converter is not used, keep the following pins connected with the level as described below.

AVcc = Vcc level

$AV_{SS} = V_{SS}$  level

- When Powering ON: Vcc→AVcc→AVRH

- When Powering OFF : AVRH→AVcc→Vcc

### **About Oscillation Input at Power On**

When turning the power on, maintain clock input until the device is released from the oscillation stabilization wait state.

### Caution for operation during PLL clock mode

On this microcontroller, if in case the crystal oscillator breaks off or an external reference clock input stops while the PLL clock mode is selected, a self-oscillator circuit contained in the PLL may continue its operation at its self-running frequency. However, Fujitsu will not guarantee results of operations if such failure occurs.

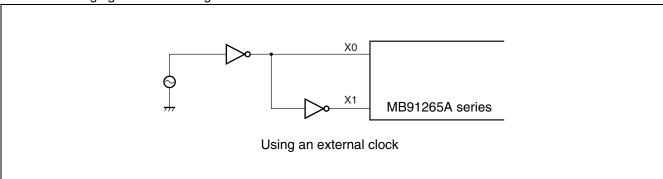

#### **External clock**

When external clock is selected, the opposite phase clock to X0 pin must be supplied to X1 pin simultaneously. If the STOP mode (oscillation stop mode) is used simultaneously, the X1 pin is stopped with the "H" output. So, when STOP mode is specified, approximately 1  $k\Omega$  of resistance should be added externally to avoid the collision of output.

The following figure shows using an external clock.

#### C pin

A bypass capacitor of approximately 0.1 µF should be connected the C pin for built-in regulator.

### **ACC** pin

A capacitor of approximately 0.1  $\mu$ F should be inserted between the ACC pin and the AVss pin as this product has built-in A/D converter.

### **Clock Control Block**

Input the "L" signal to the INIT pin to assure the clock oscillation stabilization wait time.

#### **Switch Shared Port Function**

To switch between the use as a port and the use as a dedicated pin, use the port function register (PFR) .

#### **Low Power Consumption Mode**

To enter the standby mode, use the synchronous standby mode (set with the SYNCS bit as bit 8 in the TBCR : timebase counter control register) and be sure to use the following sequence

(LDI #value\_of\_standby, R0) : value\_of\_standby is write data to STCR. #\_STCR, R12) (LDI : \_STCR is address (481H) of STCR. STB R0, @R12 : Writing to standby control register (STCR) @R12, R0 : STCR read for synchronous standby **LDUB LDUB** @R12, R0 : Dummy re-read of STCR NOP : NOP × 5 for arrangement of timing NOP NOP NOP NOP

In addition, please set I flag, ILM, and ICR to diverge to the interruption handler that is the return factor after the standby returns.

- Please do not do the following when the monitor debugger is used.

- Break point setting for above instruction lines

- Step execution for above instruction lines

### Notes on the PS register

As the PS register is processed by some instructions in advance, exception handling below may cause the interrupt handling routine to break when the debugger is used or the display contents of flags in the PS register to be updated.

As the microcontroller is designed to carry out reprocessing correctly upon returning from such an EIT event, it performs operations before and after the EIT as specified in either case.

- The following operations may be performed when the instruction immediately followed by a DIVOU/DIVOS instruction is (a) acceptance of a user interrupt, (b) single-stepped, or (c) breaks in response to a data event or emulator menu:

- 1) The D0 and D1 flags are updated in advance.

- 2) An EIT handling routine (user interrupt or emulator) is executed.

- 3) Upon returning from the EIT, the DIVOU/DIVOS instruction is executed, and the D0 and D1 flags are updated to the same values as in 1).

- The following operations are performed when the ORCCR/STILM/MOVRi and PS instructions are executed to allow the interrupt.

- 1) The PS register is updated in advance.

- 2) An EIT handling routine (user interrupt) is executed.

- 3) Upon returning from the EIT, the above instructions are executed, and the PS register is updated to the same value as in 1).

### **Watchdog Timer**

The watchdog timer built in this model monitors a program that it defers a reset within a certain period of time. The watchdog timer resets the CPU if the program runs out of controls, preventing the reset defer function from being executed. Once the function of the watchdog timer is enabled, therefore, the watchdog timer keeps on operating programs until it resets the CPU.

As an exception, the watchdog timer defers a reset automatically under the condition in which the CPU stops program execution.

For those conditions to which this exception applies, refer to " NOTE ON DEBUGGER".

#### **■ NOTE ON DEBUGGER**

#### Step execution of RETI command

If an interrupt occurs frequently during step execution, the corresponding interrupt handling routine is executed repeatedly after step execution.

This will prevent the main routine and low-interrupt-level programs from being executed.

Do not execute step of RETI instruction for escape.

Disable the corresponding interrupt and execute debugger when the corresponding interrupt handling routine no longer needs debugging.

### • Operand break

Do not apply a data event break to access to the area containing the address of a system stack pointer.

#### Execution in an unused area of flash memory

Accidentally executing an instruction in an unused area of flash memory (with data placed at 0xFFFF) prevents breaks from being accepted.

To prevent this, the code event address mask function of the debugger should be used to cause a break when accessing an instruction in an unused area.

#### Power-on debugging

All of the following three conditions must be satisfied when the power supply is turned off by power-on debugging.

- (1) The time for the user power to fall from 0.9  $V_{CC}$  to 0.5  $V_{CC}$  is 25  $\mu s$  or longer. Note: In a dual-power system,  $V_{CC}$  indicates the external I/O power supply voltage.

- (2) CPU operating frequency must be higher than 1 MHz.

- (3) During execution of user program

### • Interrupt handler for NMI request (tool)

Add the following program to the interrupt handler to prevent the device from malfunctioning in case the factor flag to be set only in response to a break request from the ICE is set, for example, by an adverse effect of noise to the DSU pin while the ICE is not connected. Enable to use the ICE while adding this program.

#### Additional location

Next interrupt handler

Interrupt source : NMI request (tool)

Interrupt number : #13 (decimal), 0D (hexadecimal)

Offset : 3C8H

Address TBR is default : 000FFFC8H

#### Additional program

STM (R0, R1)

LDI #B00н, R0; : B00н is the address of DSU break factor register.

LDI #0, R1

STB R1, @R0 : Clear the break factor register.

LDM (R0, R1)

RETI

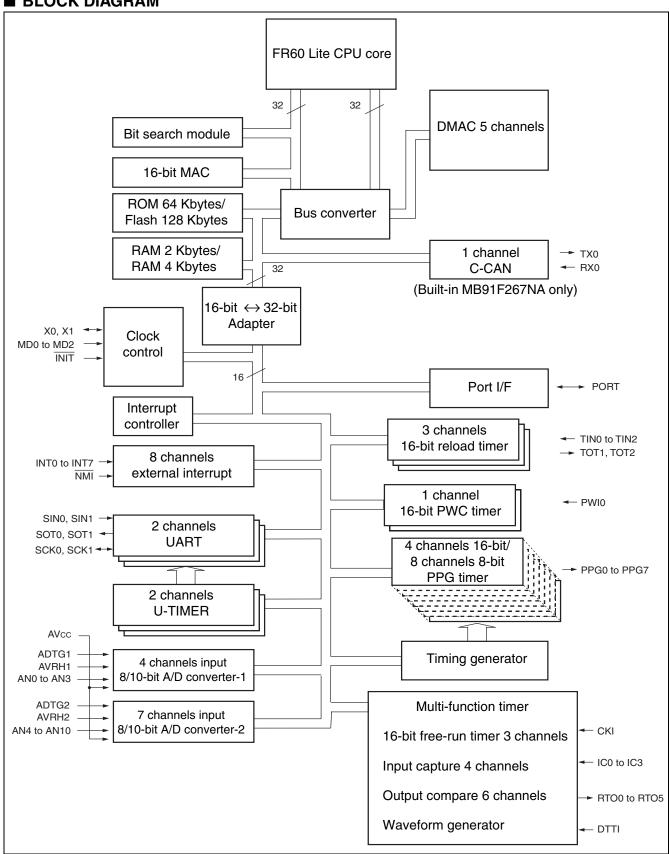

### **■ BLOCK DIAGRAM**

### **■ MEMORY SPACE**

### 1. Memory space

The FR family has 4 Gbytes of logical address space (2<sup>32</sup> addresses) available to the CPU by linear access.

### Direct Addressing Areas

The following address space areas are used as I/O areas.

These areas are called direct addressing areas, in which the address of an operand can be specified directly during an instruction.

The size of directly addressable areas depends on the data size to be being accessed as follows.

ightarrow byte data access : 000 $_{\rm H}$  to 0FF $_{\rm H}$  ightarrow half word data access : 000 $_{\rm H}$  to 1FF $_{\rm H}$  ightarrow word data access : 000 $_{\rm H}$  to 3FF $_{\rm H}$

### 2. Memory Map

| MB91F267A/               | /MB91F267NA                |                        | MB91266A                 |                           |                        |

|--------------------------|----------------------------|------------------------|--------------------------|---------------------------|------------------------|

|                          | Single chip mode           |                        |                          | Single chip mod           | le                     |

| 0000 0000н               | I/O                        | Direct addressing area | 0000 0000н               | I/O                       | Direct addressing area |

| 0000 0400H               | I/O                        | Refer to ■ I/O MAP     |                          | I/O                       | Refer to ■ I/O MAP     |

| 0001 0000н               | Access<br>disallowed       |                        | 0001 0000н               | Access<br>disallowed      |                        |

| 0003 F000н<br>0004 0000н | Internal RAM<br>4 Kbytes   |                        | 0003 F800н<br>0004 0000н | Internal RAM<br>2 Kbytes  |                        |

| 0004 0000H               | Access<br>disallowed       |                        | 0004 0000H               | Access<br>disallowed      |                        |

| 000E 0000H               | Internal ROM<br>128 Kbytes |                        | 000F 0000н               | Internal ROM<br>64 Kbytes |                        |

| 0010 0000н               | Access<br>disallowed       |                        | 0010 0000н               | Access<br>disallowed      |                        |

| FFFF FFFF <sub>H</sub>   |                            |                        | FFFF FFFF <sub>H</sub>   |                           |                        |

### **■ MODE SETTINGS**

The FR family uses mode pins (MD2 to MD0) and a mode data to set the operation mode.

• Mode Pins

The MD2 to MD0 pins specify how the mode vector fetch and reset vector fetch is performed.

Setting is prohibited other than that shown in the following table.

| M   | Mode Pins |     | Mode name                | Reset vector | Remarks                      |

|-----|-----------|-----|--------------------------|--------------|------------------------------|

| MD2 | MD1       | MD0 | access area              |              | nemarks                      |

| 0   | 0         | 0   | Internal ROM mode vector | Internal     |                              |

| 0   | 0         | 1   | External ROM mode vector | External     | Not supported by this model. |

#### Mode data

Data written to the internal mode register (MODR) by a mode vector fetch is called mode data.

After an operation mode has been set in the mode register, the device operates in the operation mode.

The mode data is set by all reset source. User programs cannot set data to the mode register.

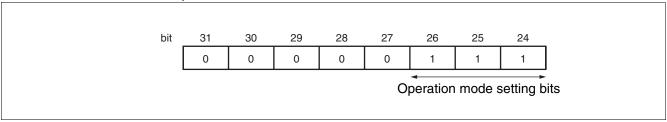

Details of mode data description

Bit31 to bit24 are all reserved bits.

Be sure to set this bit to "00000111".

Operation is not guaranteed when any value other than "00000111" is set.

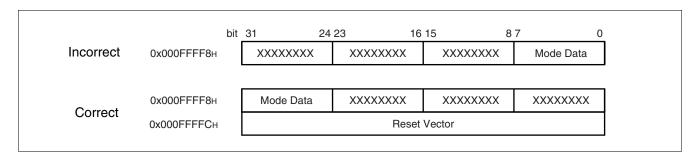

Note: Mode data set in the mode vector must be placed as byte data at 0x000FFFF8H.

Use the highest byte from bit31 to bit24 for placement as the FR family uses the big endian for byte endian.

### ■ I/O MAP

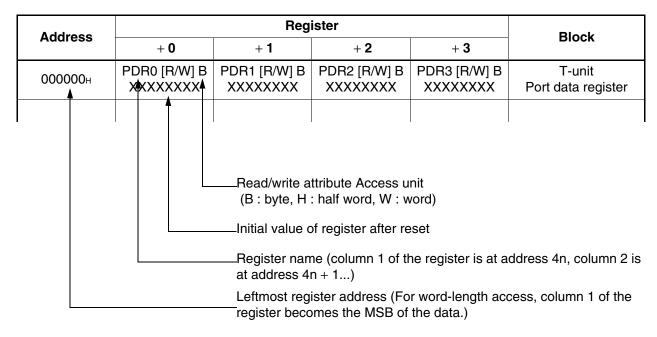

[How to read the table]

Note: Initial values of register bits are represented as follows:

" 1 " : Initial Value " 1 " " 0 " : Initial Value " 0 "

" X ": Initial Value " undefined"

" - " : No physical register at this location

Access is barred with an undefined data access attribute.

| A ddwooo                 |                                           | Block                                     |                                           |                                           |                                   |  |

|--------------------------|-------------------------------------------|-------------------------------------------|-------------------------------------------|-------------------------------------------|-----------------------------------|--|

| Address                  | + 0                                       | + 1                                       | + 2                                       | + 3                                       | Block                             |  |

| 000000н                  | PDR0 [R/W] B, H, W<br>XXXXXXXX            | PDR1 [R/W] B, H, W<br>XXXXXXXX            | PDR2 [R/W] B, H, W<br>XXXXXXXX            | PDR3 [R/W] B, H, W<br>XXXXXXXX            |                                   |  |

| 000004н                  | PDR4 [R/W] B, H, W<br>-XXXXXXX            | PDR5 [R/W] B, H, W<br>XXXXXXXX            | _                                         | _                                         | Port data                         |  |

| 000008н                  | _                                         | _                                         | _                                         |                                           |                                   |  |

| 00000Сн                  | _                                         | _                                         | _                                         | _                                         |                                   |  |

| 000010н                  | PDRG [R/W] B, H, W                        | _                                         | _                                         | _                                         |                                   |  |

| 000014н<br>to<br>00003Сн |                                           | _                                         |                                           |                                           | Reserved                          |  |

| 000040н                  | EIRR0 [R/W] B, H, W<br>00000000           | ENIR0 [R/W] B, H, W<br>00000000           |                                           | W] B, H, W<br>00000000                    | External interrupt (INT0 to INT7) |  |

| 000044н                  | DICR [R/W] B, H, W HRCL [R/W, R] B, H, W0 |                                           | Delay interrupt/<br>Hold request          |                                           |                                   |  |

| 000048н                  | TMRLR0<br>XXXXXXXX                        | R] H, W<br>XXXXXXXX                       | Reload                                    |                                           |                                   |  |

| 00004Сн                  | -                                         | -                                         | TMCSR0 [R/W, R] B, H, W<br>00000 00000000 |                                           | timer 0                           |  |

| 000050н                  | TMRLR1<br>XXXXXXXX                        |                                           | TMR1 [R] H, W<br>XXXXXXXX XXXXXXX         |                                           | Reload                            |  |

| 000054н                  | -                                         | -                                         |                                           | TMCSR1 [R/W, R] B, H, W<br>00000 00000000 |                                   |  |

| 000058н                  | TMRLR2<br>XXXXXXXX                        |                                           | TMR2 [R] H, W<br>XXXXXXXX XXXXXXX         |                                           | Reload                            |  |

| 00005Сн                  | _                                         | -                                         |                                           | W, R] B, H, W<br>00000000                 | timer 2                           |  |

| 000060н                  | SSR0 [R/W, R] B, H, W<br>00001000         | SIDR0 [R]/SODR0[W]<br>B, H, W<br>XXXXXXXX | SCR0 [R/W] B, H, W<br>00000100            | SMR0 [R/W, W]<br>B, H, W<br>000-0-        | UART0                             |  |

| 000064н                  | UTIM0 [R] H /<br>00000000                 |                                           | DRCL0 [W] B                               | UTIMC0 [R/W] B<br>000001                  | U-TIMER 0                         |  |

| 000068н                  | SSR1 [R/W, R] B, H, W<br>00001000         | SIDR1 [R]/SODR1[W]<br>B, H, W<br>XXXXXXXX | SCR1 [R/W] B, H, W<br>00000100            | SMR1 [R/W] B, H, W<br>000-0-              | UART1                             |  |

| 00006Сн                  | UTIM1 [R] H / 00000000                    |                                           | DRCL1 [W] B                               | UTIMC1 [R/W] B<br>000001                  | U-TIMER 1                         |  |

| 000070н<br>to<br>00007Сн | _                                         | _                                         | _                                         | _                                         | Reserved                          |  |

| A dduooo | Register                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                 |                                  |                            |  |  |  |  |

|----------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|----------------------------------|----------------------------|--|--|--|--|

| Address  | + 0                                                                                                          | + 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | + 2                             | + 3                              | Block                      |  |  |  |  |

| 000080н  | ADCH1 [R/W] B, H, W<br>XXXX0XX0                                                                              | ADMD1 [R/W] B, H, W<br>00001111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ADCD11 [R] B, H, W<br>XXXXXXXX  | ADCD10 [R] B, H, W<br>XXXXXXXX   | A/D                        |  |  |  |  |

| 000084н  | ADCS1 [R/W, W] B, H, W<br>00000X00                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                 | _                                | converter 1/<br>AICR1      |  |  |  |  |

| 000088н  | ADCH2 [R/W] B, H, W<br>XXXX0XX0                                                                              | ADMD2 [R/W] B, H, W<br>00001111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ADCD21 [R] B, H, W<br>XXXXXXXX  | ADCD20 [R] B, H, W<br>XXXXXXXX   | A/D<br>converter 2/        |  |  |  |  |

| 00008Сн  | ADCS2 [R/W, W] B, H, W<br>00000X00                                                                           | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | AICR2 [R/W] B, H, W<br>-0000000 | _                                | AICR2                      |  |  |  |  |

| 000090н  | OCCPBH0, OCCPBL0[W] / OCCPBH1, OCCPBL1[W] / OCCPH0, OCCPL0[R] H, W O0000000 00000000 00000000 000000000 0000 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                 |                                  |                            |  |  |  |  |

| 000094н  | OCCPH2, OCC                                                                                                  | OCCPBH2, OCCPBL2[W] / OCCPBH3, OCCPBL3[W] / OCCPH2, OCCPL2 [R] H, W OCCPH3, OCCPL3 [R] H, W OCCPH3, OC |                                 |                                  |                            |  |  |  |  |